1.1.2 四线

题目描述

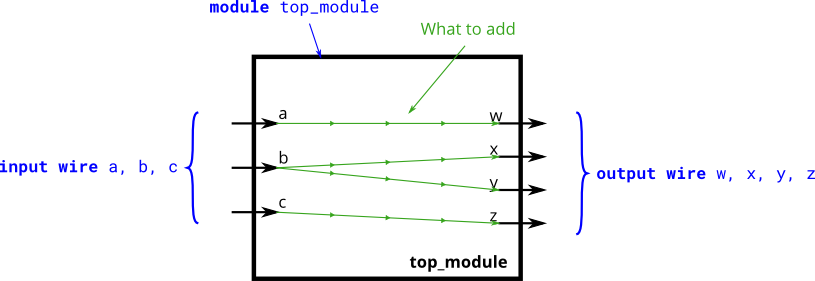

以下是一个具有3个输入和4个输出的模块,其行为类似于进行以下连接的电线:

a -> w

b -> x

b -> y

c -> z

下面的图示说明了电路的每个部分如何与Verilog代码中的每个位相对应。从模块外部来看,有三个输入端口和四个输出端口。

当有多个赋值语句时,它们在代码中的显示顺序无关紧要。与编程语言不同,赋值语句(“连续赋值”)描述的是事物之间的联系,而不是将值从一个事物复制到另一个事物的操作。

现在也许应该澄清的一个潜在的混淆来源:这里的绿色箭头代表 电线之间的连接,但本身不是电线。模块本身已经声明了7根电线(命名为 a、b、c、w、x、y 和 z)。这是因为和声明 除非另有说明,否则实际声明电线。写 input wire a 和写 input a相同。因此,这些语句不是在创建电线,而是在创建之间的连接已经存在的7根电线。

模块声明

module top_module(

input a,b,c,

output w,x,y,z );